Superfin corp

At superforex we are committed to developing and implementing top-notch technologies and a high level of services to satisfy even the most demanding traders.

Actual forex bonuses

As we recognize the importance of doing business in a safe and stable environment, all of our activities are based on transparency and honesty. Account parameters:

broker type: market maker

account types: standard

MAM/PAMM accounts: yes

min. Deposit: $1

minimum lot size: FX 0.01

max leverage: 1:1000*

spread type: fixed

execution type: market

payment options:credit/debit card, wire transfer, SKRILL, neteller, payco, bitcoin, astropay, webmoney and sorexpay, among others

withdrawal options: same as deposited

accept US clients: no

Superforex – superfin corp

Why choose us

Professional services, innovation in technologies, openness and compliance – those are just some of the reasons behind our customers’ choice. It is our passion and devotion to the business and industry that make us different from our competitors.

At superforex we are committed to developing and implementing top-notch technologies and a high level of services to satisfy even the most demanding traders. As we recognize the importance of doing business in a safe and stable environment, all of our activities are based on transparency and honesty.

We provide our customers with a large selection of financial services and investment products to trade successfully with and offer a variety of trading options designed to suit the needs of both private and corporate clients.

All financial and brokerage services of superforex are globally regulated by the international financial services commission. If you have any further questions about our regulation, you can contact the IFSC at info@ifsc.Gov.Bz.

We provide our traders with a wide range of financial instruments for algorithmic or self-trading, money management and investment. Our advanced technology allows for instant trading execution.

Brokerage info:

legal name: superfin corp

operational since: 2013

domiciled country: belize

headquarters city: belize

international offices: N/A

regulation: IFSC

monthly volume in USD: undisclosed

number of liquidity providers: 3

managed account services: yes

markets/instraments: forex, cfds, futures, indices

parent/subsidiary/affiliations: owned by vantage global prime pty ltd

Account parameters:

broker type: market maker

account types: standard

MAM/PAMM accounts: yes

min. Deposit: $1

minimum lot size: FX 0.01

max leverage: 1:1000*

spread type: fixed

execution type: market

payment options:credit/debit card, wire transfer, SKRILL, neteller, payco, bitcoin, astropay, webmoney and sorexpay, among others

withdrawal options: same as deposited

accept US clients: no

Trading features:

currency pairs total: 300+ pairs

trading platforms:metatrader 4, webtrader, MT4 mobile app (ios, android)

commission fees: no

news trading: yes

mirror/social trading: no

scalping: no

hedging: yes

expert advisors: yes

swap free: yes

API support: yes

OCO orders: no

Superforex – superfin corp

Why choose us

Professional services, innovation in technologies, openness and compliance – those are just some of the reasons behind our customers’ choice. It is our passion and devotion to the business and industry that make us different from our competitors.

At superforex we are committed to developing and implementing top-notch technologies and a high level of services to satisfy even the most demanding traders. As we recognize the importance of doing business in a safe and stable environment, all of our activities are based on transparency and honesty.

We provide our customers with a large selection of financial services and investment products to trade successfully with and offer a variety of trading options designed to suit the needs of both private and corporate clients.

All financial and brokerage services of superforex are globally regulated by the international financial services commission. If you have any further questions about our regulation, you can contact the IFSC at info@ifsc.Gov.Bz.

We provide our traders with a wide range of financial instruments for algorithmic or self-trading, money management and investment. Our advanced technology allows for instant trading execution.

Brokerage info:

legal name: superfin corp

operational since: 2013

domiciled country: belize

headquarters city: belize

international offices: N/A

regulation: IFSC

monthly volume in USD: undisclosed

number of liquidity providers: 3

managed account services: yes

markets/instraments: forex, cfds, futures, indices

parent/subsidiary/affiliations: owned by vantage global prime pty ltd

Account parameters:

broker type: market maker

account types: standard

MAM/PAMM accounts: yes

min. Deposit: $1

minimum lot size: FX 0.01

max leverage: 1:1000*

spread type: fixed

execution type: market

payment options:credit/debit card, wire transfer, SKRILL, neteller, payco, bitcoin, astropay, webmoney and sorexpay, among others

withdrawal options: same as deposited

accept US clients: no

Trading features:

currency pairs total: 300+ pairs

trading platforms:metatrader 4, webtrader, MT4 mobile app (ios, android)

commission fees: no

news trading: yes

mirror/social trading: no

scalping: no

hedging: yes

expert advisors: yes

swap free: yes

API support: yes

OCO orders: no

Intel announces 10nm superfin transistor – roughly the same level of performance uplift as A node shrink

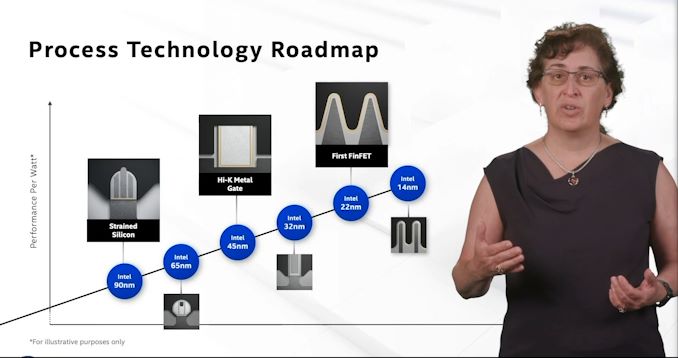

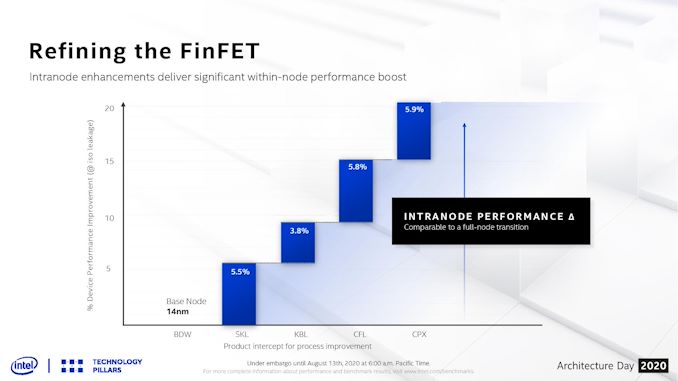

Intel held its architecture day 2020 for the press on august 11 and revealed quite a few technological innovations but the star of the show for architecture fans was the company's superfin process enhancement. Intel joked about their ++++ improvements on 14nm and revealed a new finfet type for 10nm called superfin which allowed them to gain several plusses worth of improvement in one go. According to intel and the benchmarks they provided, the improvement in performance is roughly equal to one node shrink.

Intel's 10nm superfin transistor achieves

17.5% performance uplift and significantly higher clock speeds compared to vanilla 10nm

Intel's 10nm has gained quite a reputation for being broken but it looks like the company has not only managed to fix problems with the original 10nm process but improve it to get several iterations worth of performance uplift in a single go. A single "+" iteration previously gave a performance uplift of around 5% but with 10nm superfin enhanced, the intranode performance uplift is roughly 17.5% when compared to vanilla 10nm.

Before we go any further, here is an introduction to intel's 10nm superfin from ruth brian herself:

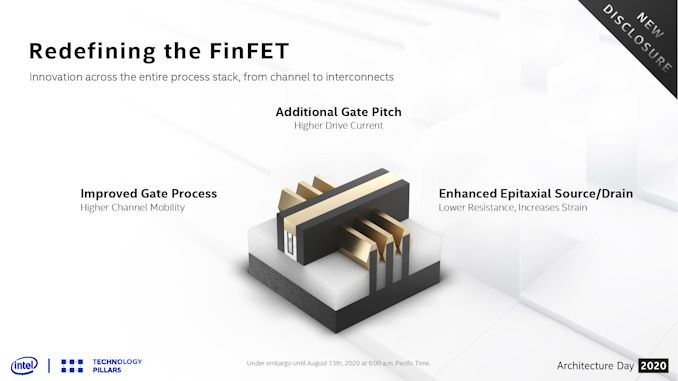

We are redefining [the finfet] to deliver an unprecedented level of performance uplift. We achieve this through a combination of innovations across the entire process stack from the bottom of the transistor channel all the way to the top interconnect metal layers. Within the transistor, we improved epitaxial growth of crystal structures on the source and drain, increasing the strain and reducing resistance. It allowed more current to flow through the channel.

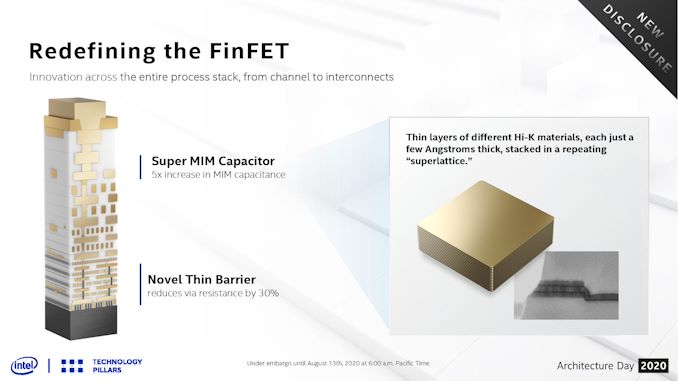

We had an enhanced source drain architecture driving additional higher channel mobility and enabling charge carriers to move more quickly. Additionally, we had a gate pitch that we've included to provide higher drive currents for certain chip functions that require the utmost performance. Moving up to the metal stack a new thin barrier reduces via resistance by up to 30% enhancing interconnect performance.

The final innovation is a new super MIM metal insulator metal capacitor when compared to the industry standard, it delivers a 5x increase in capacitance within the same footprint driving a voltage reduction that translates to dramatically improved product performance. This is an industry first technology that far exceeds the current capabilities of other manufacturers. This innovation is enabled by a new class of high-k dielectric materials stacking ultra thin layers just several angstroms thick to form a repeating super lattice structure.

The combined power of these innovations enable us to deliver a dramatic process performance boost that makes it the largest single node enhancement in intel history. In one single internode enhancement we delivered essentially the same level of performance achieved over multiple steps at 14 nanometer and nearly the equivalent performance of a full node transition. This process boost will take intel products to a new level in 2020 and beyond. – ruth brian, intel fellow, architecture day 2020.

Here are some interesting tidbits about intel's superfin transistor:

- Intel's superfin transistor was first developed when trying to fix 10nm and was initially named 10nm+. Intel realized however, that since previous "+" iterations had only achieved 1/3 of the performance uplift, this was better served with its own proper name.

- Intel's tiger lake processors are based on superfin technology and are able to achieve astonishingly high clock rates for a 10nm chip. You can read more about that in our deep dive by clicking the link.

- Intel's ice lake processors are based on vanilla 10nm and not superfin.

- The company is already working on superfin enhanced but has not named that yet.

To prove its point, intel showed benchmarks with all the "+" iterations of 14nm detailed. Each plus got roughly around a 5% improvement compared to the previous node. Intel's 10nm superfin on the other hand achieves more than three times that amount in one go. And that's not all! Intel is already working on a superfin enhanced transistor that they have yet to name properly.

Here is intel's ruth brian on the subject of superfin enhanced:

Our friends in the datacenter saw what we were developing with the new super fin technology with the client group. They asked us to make some further enhancements for data center products specifically. Servers benefit from interconnect enhancements to the large amount of data that needs to be shared across the chip. So in addition to continue transistor optimization to deliver more internode performance, we also focused on improving the metal staff with interconnect layer optimizations that make data center scale fabrics for CPU and GPU more easily routable. We’ll have a lot more to say about this enhanced technology in the near future. – ruth brian, intel fellow, architecture day 2020.

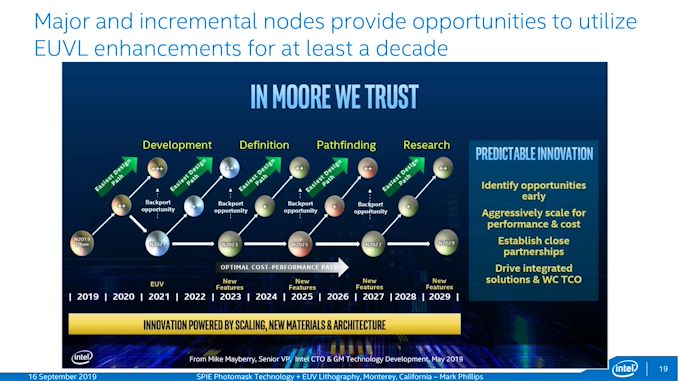

Intel's path forward: 10nm superfin technology, advanced packaging roadmap

Intel's architecture day 2020 was awash in new revelations, you can find the full breakdown here, but its new 10nm superfin technology and advanced packaging technology rank among the highlights. Both of these technologies will be critical factors as the chipmaker looks to defray the impact from the fallout of its delayed 7nm node.

Intel says the new 10nm superfin technology provides the largest intra-node performance improvement in the company's history, giving its forthcoming chips higher frequencies and lower power consumption than the first version of its 10nm node. That's a critical need because the company had originally planned for a rapid transition to its 7nm process, leaving its generally unproductive and troublesome 10nm node in the rearview mirror while reserving the node for only a few products as the company quickly moved forward to what it saw as the better node.

That rapid transition is obviously delayed now that intel has identified a 'defect mode' in its 7nm process that puts it a year behind its yield targets. Intel says that, due to a buffer designed into its roadmap, the year-long recovery translates to a six-month delay in 7nm products reaching the market. However, intel hasn't specified whether or not those first 7nm products will come with its own process node, or instead from chips bought from external foundries. The latter is a new possibility now that intel has new plans to more aggressively leverage external fabs. That could even result in it using other fabs for its core logic, like cpus and gpus, which the company hasn't done in the past.

To help blunt the blow of the 7nm delay, intel announced that it would boost its 10nm production by 20% over its prior projections and said it planned to wring out another "full node" of performance from the troubled node. It also plans to leverage its advanced packaging technology to rapidly integrate chips produced at third-party foundries into its own products. Both of these technologies are going to be incredibly important as intel strives to remain competitive in the face of ever-growing pressure from all sides in its key money-making segments; the desktop PC and data centers. Both segments are now under attack from a resurgent AMD and the burgeoning ARM ecosystem.

Intel's 10nm superfin technology

Intel's plans to wring out more performance from its 10nm aren't entirely surprising - the company learned the value of inter-node improvements the hard way during its incessant 10nm delays. Through a long string of "+" revisions to its 14nm node, with each step powering performance enhancements throughout the skylake, kaby lake, coffee lake and cooper lake iterations of intel's chips. Each intra-node step yielded a 3.8% to 5.9% improvement in transistor performance at iso leakage, which translates to tangible performance benefits that helped intel remain competitive despite its continuous 10nm delays. In fact, intel claims that it has extracted nearly enough extra performance from 14nm as it has historically gotten from a move to a new, denser process node.

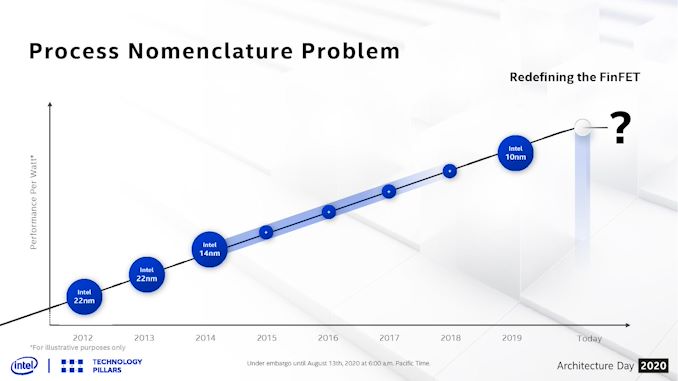

After four intra-node enhancements, much to the amusement and confusion of industry observers, intel is now on its 14nm++++ node. Intel obviously didn't plan for this many iterations of the node when it first slapped the "+" branding on its first 14nm enhancement, and the scheme has become more than unwieldy. In fact, due to rampant confusion about the naming scheme, including among intel's own teams, the company will now assign a new unique name to each process node.

"10nm superfin" marks the first outing for its new terminology, but intel says the node is the equivalent of a 10nm+ revision. Intel says that the name "superfin" comes from a combination of supermim, one of the key ingredients to the design that we'll cover below, and finfet, which is intel's term for its first 3D transistor design that debuted three generations ago and carries on to today.

Intel's inaugural 10nm node encountered plenty of problems, necessitating a lengthy redesign process to fix several not-yet-explained issues. Intel tells us that its currently-shipping version of 10nm still uses cobalt, contact over active gate (COAG), and self-aligned quad patterning (SAQP). This trio of new technologies enabled a 2.7X density improvement over 14nm, but have been rumored to be the source of intel's delays.

Intel's 10nm superfin builds on those technologies with several steps forward of its own. Intel improved the gate pitch to enable higher drive current for some high-speed functions, and enhanced epitaxial growth on the source and drain elements helps lower resistance and improve strain. That helps more current flow through the channel, allowing charge carriers to move more quickly.

The 10nm superfin transistors have a new thin barrier that reduces interconnect resistance by 30%, which improves interconnect performance - a critical factor as interconnects continue to shrink and become one of the largest barriers to chip scaling. Intel claims the supermim (metal-insulator-metal) capacitor brings a 5X improvement in MIM capacitance compared to the "industry standard" devices that have the same footprint. This helps combat vdroop, which helps ensure longer sustained frequency potential. Intel says it used new hi-K materials stacked in a repeating superlattice structure, and also added two high-performance layers to the top of the stack. The changes don't impact density, but have a big impact on performance.

The 10nm superfin transistors offer higher clock speeds at any given voltage, and can operate at a lower voltage at any given frequency. The transistors also have a greater dynamic range from the vmin to vmax (minimum/maximum voltage), and vmax extends further than found with the original 10nm transistors. By tuning the architecture to exploit the full dynamic range of the transistors, intel claims tiger lake offers both higher maximum frequencies in thermally-unconstrained use and is faster and more efficient in TDP-limited environments. Intel says the culmination of the tuning imparts a greater-than-generational performance improvement from the marginally IPC-optimized willow cove core over the sunny cove cores present in ice lake.

Intel says the net effect is the same amount of performance uplift that the company would normally expect from a whole series of intra-node "+" revisions, but with just one iteration. Intel claims these transistors mark the largest single intra-node improvement in the company's history.

Intel famously encountered issues with its original 10nm node that necessitated a redesign, so speculation will run rampant that many of the new features are merely borne of the need to fully correct the issues that hindered first-gen 10nm's performance and profitability.

Regardless, intel claims to have gained a step-function improvement in the 10nm process node, and the improvements have caught the attention of the company's data center architects. Koduri said that the company is working on a new tentatively-named "enhanced superfin" process, optimized specifically for the data center, that will bring about further performance and interconnect improvements. The latter is an important consideration for data center chips that rely on the utmost bandwidth between compute-heavy cores and heavily-utilized I/O interfaces.

Intel says this process tech will debut with the company's rambo cache in its xe ponte vecchio cards and its sapphire rapids data center chips.

Decoupling architecture from process nodes

Intel's struggles with its 10nm node led the company to rethink its approach to chip design completely. In the past, intel's design methodology was focused on single-die monolithic designs with architectures tightly coupled and tuned to each specific process node. Unfortunately, this left the chipmaker exposed to the fallout of any delays in its race to smaller, denser nodes.

Intel is frank that the deep bonds between architectures, IP, and specific process nodes cost it the ability to bring new architectures, like sunny cove, to market within a reasonable time frame. Intel also lost the ability to introduce critically important new features in a timely fashion, like pcie gen 4, creating deficiencies in its product stack. The lack of flexibility also delayed the rapid development of newer types of products, like its xe graphics. The tight coupling between architecture and process nodes also made it nearly impossible to port those designs over to older process nodes, or to shift its designs to nodes from other foundries.

Intel's initial set of contingency plans marked a transformational change to the company's design methodologies. First, intel committed itself to decoupling its architectures from the process, thus making its architectures portable between nodes. This new approach allows the chipmaker to use newer architectures on older nodes, thus speeding deployment in the face of unanticipated delays. It also allows intel to select the best node for the intended purpose, be it either an internally-developed node, or a node from an external vendor.

These changes do result in sacrificing some level of deep architectural tuning for each process node, which in turn results in less performance-enhancing customizations. However, the net effect is a faster, more flexible design process that allows the company to sidestep challenges with its process tech.

Intel’s 11th gen core tiger lake soc detailed: superfin, willow cove and xe-LP

What is 10nm superfin all about?

For those within the semiconductor industry, as well as individuals with investments in the companies we cover, it has been hard to miss the recent news surrounding intel’s manufacturing process woes. In short, intel’s 10nm process technology has failed to match expectations in performance and yield, coming in a couple of years later than expected and with an inability to compete with its own previous generation products. It still remains in low volume today, with tiger lake expected to be the first true example of what intel’s vision 10nm was meant to be.

The next step function change in intel’s manufacturing, the move to 7nm using extreme ultra violet (EUV) technology, has recently been announced that it also has an additional six month delay. With news like this, it has become a struggle to remain confident about intel’s ability to deliver an industry-leading manufacturing node technology that is competitive in the market. This used to be the position that intel held until delays crept into the 10nm process.

Intel’s ruth brain, senior transistor architect, covering intel’s engineering feats

Intel’s disclosures on its manufacturing technology vary in complexity depending on how successful the product is perceived internally. When intel first announced finfets on its 22nm process node, in may 2011, there was a lot of information straight out of the gate, and the node was very successful. With the next generation of 14nm, there were some delays with the initial generation of broadwell products, but ultimately the process was explained in detail by the company at its own event and we published our article on 14nm in august 2014. The 14nm process node has been intel’s most profitable manufacturing node to date, and continuous intranode enhancements over the years (14+, 14++, 14+++, 14++++*) have given the company an effective enhancement equivalent to a pure node update within a manufacturing generation.

*yes, intel has a 14++++ node. It’s even in their diagrams. The only product confirmed to be on 14++++ as far as we can tell is the cooper lake xeon scalable family.

When it comes to 10nm, the situation is not as rosy, even compared to the delays on 14nm. To date, intel has had two generations of 10nm products on the CPU side, one of which the company steers away from even trying to mention it in public, even though we’ve reviewed it in excruciating detail.

Cannon lake, the first 10nm product, found its way into intel’s crimson canyon NUC mini-pcs and was a hot mess: two cores only, disabled integrated graphics, and although it shipped for revenue in 2017, intel was right to consign it to history very quickly.

Ice lake was intel’s proper launch vehicle for 10nm, offering four cores and a lot of gen11 graphics within 15 watts. It has found its way into over 50 laptop designs, but as mentioned on the previous page, despite its 15-20% increase in raw performance clock-for-clock, that 10-20% decrease in frequency balances it out for a minimal CPU improvement over 14nm. The graphics on ice lake are still a lot better than on 14nm, and support for thunderbolt 3 as well as 512-bit vector instructions means that ice lake still has a few plus points.

As it stands, because intel doesn’t want to consider cannon lake as a true part of its heritage, ice lake was deemed a flat ‘10nm’ product, with no plusses and no extra bits. After ice lake was set to be tiger lake, built on a ‘10+’ manufacturing node.

+, ++, +++, ++++: what is a name

A side note about manufacturing process naming. As many of our readers are aware, the actual number attached to the process in the era of finfet technology has effectively become nothing more than a proper noun for the process node technology – it isn’t related to any feature within the products built on that process. It gets especially confusing when there are features of a process built at a smaller scale than the number on the technology: for example, intel’s 10nm actually has features that are 8nm in size. Manufacturing nodes might as well be given names like gordon, eric, or lisa, in order to stop the confusion that having that number provides.

Within a generation of a process node technology, the company fabricating the semiconductor orders may periodically update its manufacturing process but still keep it, by and large, within the confines of that generation. These updates are often minor, but are called BKM (best-known-method) updates and can lead to simple frequency or power efficiency improvements – perhaps on the order of 50 mv or 25 mhz, but sometimes afford bigger gains.

When we were dealing with planar transistors, at 22nm, 32nm, 45nm and above, these BKM updates were par for the course during the lifecycle of a product built at that node. Improvements in the manufacturing were taken, rolled into the product automatically, and it was simply sold in the same box without much of a fuss, but had marginally better characteristics.

As we’ve moved into multiple generations of finfet technologies, where creating a leading edge high-performance processor can cost $10-$100million or more, these BKM updates have become marketable updates to both the chip design companies and the fabs they are built on. Small tweaks to the BKM are now being used to launch new waves of products, and offer the companies involved a chance to create column inches and highlight the engineering prowess of the teams involved, as well as offering the customer a better product.

Different fabrication plants have marketed these updates in different ways. Intel has gone with the +,++,+++,++++ nomenclature for its 14nm process, with each step giving better transistor device performance and being rolled into new generations of products:

However, intel’s naming scheme has become somewhat of a meme and a joke over the past few years. With the company’s inability to bring out 10nm on its initial schedule, intel decided to add more + to each new process update on 14nm. As 10nm was delayed further, consumers and users saw another + added to 14nm. The meme of intel unable to get 10nm working and seeing a 14+++++++++ future product is a fundamental strike to the soul of a company that has spent the last 30+ years priding itself on its ability to drive leading edge semiconductor manufacturing for high-performance.

As intel has slowly moved onto its 10nm product portfolio, the + naming came in again almost immediately. 10nm for cannon lake, 10+ for ice lake which later became just ‘10nm’, 10+ for tiger lake, and then 10++ and 10+++ were all exhibited on roadmaps at various industry events. The same story goes on for future processes, such as 7nm and 5nm.

If it makes you feel any better, intel’s own engineers said that even they sometimes have difficulty remembering which + variant has specific updates, or which product is built on which + node. Ultimately, while the + serves a purpose, it has ultimately become confusing for customers and engineers alike.

This is why, behind the scenes, we have told intel that it has to move away from + and ++ and +++, if only from a corporate image standpoint. Where its manufacturing competitors like TSMC and samsung can point to different variants of their 10nm processes for different products, all intel has is more pluses.

Other press and analysts have told intel this too. However, based on previous experiences, we rarely get to speak to the people who actually can cause direct change. All our contacts can do is try, and pass our comments up the chain, hopefully with as much passion as we have. The people that can actually sign off on changes like this are often not very press facing.

But someone, somewhere at intel, has finally heard our pleas. Today intel is approaching its 10nm portfolio from a different angle. While nothing is technically changed under the hood, the new strategy allows the company to market its manufacturing and products from an initial context of the deep engineering portfolio and research that occurs. The first result of this change is the superfin.

Intel 10SF: the largest single intranode enhancement in intel history

10nm superfin is what tiger lake is built on, and represents the new name for 10+. As part of intel’s 10SF, we’re getting a glimpse into what makes 10SF different to the 10 for ice lake , as well as updates on some key parts to the design of the transistors and metal stack that make up the 10SF process.

10SF builds on 10nm by introducing a redefined finfet design (intel’s 4 th gen finfet?) with increased fin performance, as well as a new supermim (metal-insulator-metal) capacitor design.

The updated finfet design focuses on three areas.

Through new manufacturing techniques, the epitaxial growth of crystal structures on the source and drain has been enhanced, ultimately increasing the strain in order to lower the resistance allowing more current to flow through the channel.

An enhanced source/drain architecture and improved gate manufacturing process helps drive additional higher channel mobility, which enabling charge carriers to move more quickly and improves transistor performance.

Additionally a larger gate pitch to enable higher drive current for certain chip functions that require the most performance. Normally a larger gate pitch sounds the opposite of what we want for a dense process node technology, however it was explained that in this case making the transistor bigger with improved performance actually means that fewer buffers are needed in the high performance cell libraries, and ultimately the cell size decreases as a result. Note that on some of intel’s 14nm variants, one of the techniques used to help drive higher frequency was a larger gate pitch.

For the metal stack, intel makes some very bold claims with impressive technology.

At the lower layers of the stack, intel is introducing a new set of barrier materials to enable thinner barriers, which also helps reduce resistance of vias by up to 30% by enabling the metal each via to be a bigger proportion of the fixed size. Reducing the resistance enhances the performance of the interconnect between the metal layers

At the higher levels, intel is introducing a new supermim (metal-insulator-metal) capacitor. Intel states that this new design gives a 5x increase in capacitance over an industry standard MIM cap within the same footprint. This drives a voltage reduction that ultimately leads to drastically improved product and transistor performance. Intel states that this is an industry first/leading design, enabled through careful deposition of new hi-K materials in thin layers, smaller than 0.1nm, to form a superlattice between two or more material types.

All combined, intel’s senior transistor architect, ruth brain, states that these features enable the ‘largest single (intra)node enhancement in intel history’, enabling 17-18% better transistor performance from the base 10nm designs. This makes 10SF equivalent to a full node enhancement over intel’s base 10nm process. To draw parallels to intel’s 14nm, 10SF to 10 is the equivalent of coffee lake (14+++) to broadwell (14nm).

Beyond superfin to enhanced superfin

As part of architecture day 2020, intel also stated that the intranode update beyond 10SF will be called 10ESF, or 10 enhanced superfin. No specific details were given as to what 10ESF will provide over 10SF, only that it will bring additional performance and interconnect innovations.

That being said, intel stated that it would be optimized for the datacenter, which likely means that some characteristics will be changed in order to support the increased thermal and current density that comes with vector acceleration. Intel, perhaps accidentally, confirmed to us that there will be three products based on 10ESF.

| Products using intel 10SF and 10ESF | |

| 10SF | tiger lake xe-LP (SG1, DG1) xe-HPC ponte vecchio active interposer tile |

| 10SFE | xe-HP xe-HPC ponte vecchio rambo cache tile sapphire rapids |

(intel has stated that ponte vecchio will have four types of tile: base, compute, rambo cache, and xe link. The others not mentioned will be split between 7nm and external fabs. More on that info in a separate article)

Intel replaces 10+ with tweaked superfin technology

By dick james, contributing editor

Intel held their virtual 2020 architecture day on august 13 th , hosted by raja koduri, and the first major topic was process innovations, with ruth brain as the presenter. Ruth started with a potted history of intel processing, from the first strained channel at the 90-nm node to the string of 14-nm evolutions.

As we know, with the delay in yielding 10-nm, the 14-nm generation had four additional inconveniently named sub-nodes (14+ → 14++++), which actually boosted performance by more than 20%, equivalent to a full node progression.

Then a quick review of 10-nm so far, with its ambitious hyper-scaling factor of 2.7; as ruth said, “it’s really no secret that we have had challenges bringing this process into production”. Comparing the cannon lake and ice lake 10-nm parts, techinsights revealed at their IEDM reception last year that there were initial problems in the middle-of-line (MOL) and the contact-over-active-gate (COAG) parts of the 10-nm process.

Ruth further stated that “ultimately we overcame these challenges and have introduced multiple products on this technology platform”, and indeed there are 18 versions of ice lake, lakefield, and snow ridge listed on the intel ark product listing website (at the time of writing). So presumably the SAQP, COAG, and cobalt will stay as part of the what is now the base 10-nm process.

Superfin transistor

Now we get to the meat of her talk – the updated “superfin” technology. I took the trouble to transcribe what she said:

“within the transistor, we improved epitaxial growth of crystal structures on the source and drain, increasing the strain and reducing resistance. It allowed more current to flow through the channel. We had an enhanced source/drain architecture driving additional higher channel mobility, enabling charge carriers to move more quickly. Additionally, we had a gate pitch that we have included, to provide higher drive current for certain chip functions that require the utmost performance.”

In a later session discussing tiger lake, boyd phelps gave us his spin on superfin:

“we added a new high-performance transistor that increases drive current with an improved gate process enabling higher mobility while also lowering the source/drain resistance, and we did this all with lower capacitance.”

Parsing these two statements, it seems we have some process tweaks in the front end:

- Modified epitaxial growth of the source and drain, increasing strain and reducing resistance;

- Enhanced source/drain architecture to give higher mobility;

- An updated gate process also increasing mobility;

- Lower capacitance in the transistor structure

All of which gives me the irresistible urge to speculate what those changes might be!

Let’s take them in the above sequence, starting with the modified epi. For PMOS, the ge content in the sige source/drains is already 50% or greater, and it seems unlikely that you could cram much more in without increasing the risk of creating lattice defects at the si/sige interface.

However, the ge content that I’ve seen is usually graded, with the maximum at the contact, and noticeably less at the interface. Changing the epi growth to put more ge closer to the interface should increase the channel strain. It’s lost in the mists of time now, but one of the original reasons for going to e-sige was that it allows higher boron doping, so in addition to increased strain, increased ge could also enable an incremental boost to the S/D doping level.

When it comes to NMOS it has never been established that intel has used carbon doping in the source/drains to induce tensile stress, but if they have now managed that, it will enhance NMOS mobility. The original technique of silicon nitride sidewall-induced tensile stress has been virtually eliminated since there is so little of it there, now we are down to

Epitaxial architecture is specifically mentioned, which makes me wonder if the S/D cavity etch has been altered to give a more ∑-etched cavity, putting the sige/si:C closer to the channel, again upping the strain and thus mobility. Not easy to do in a fin

6-7 nm thick, but it should work.

Boyd phelps mentioned “an improved gate process enabling higher mobility”; I can’t think of how the gate stack itself can increase mobility, unless somehow the gate fill could build z-stress into the gate, but in a 16-18 nm gate length there’s not much room for stressor materials.

Thinking back to planar days, strain was “memorized” in the channel by using a sacrificial layer of stressed nitride before the source/drain engineering; maybe in the polysilicon dummy gate process, before S/D formation, intel have found a way to memorize stress in the channel, to add to the S/D generated stress.

Capacitance has also been lowered – that could be a result of the larger gate pitch mentioned, but we could also have sidewall spacers with a lower dielectric constant, or even air gaps – IBM had a paper at this year’s VLSI describing a 15% reduction in ceff [1], and samsung used them in their 20-nm DRAM technology [2].

Air gaps in finfet (left) and DRAM structures [1,2]

There are other changes that could have been introduced that are not mentioned, such as taller fins (perhaps unlikely since we are already over 50 nm), and/or sige fins for PMOS, though I would think that’s more likely at 7-nm.

The 10-nm base process was announced [3] with six vt options, and boyd phelps also claimed that the introduction of the new high-performance transistor allowed some of the existing high-vt devices to be tweaked to run at higher frequency with lower leakage, so their operating voltage could be reduced, making more power available for high-performance sectors.

Superfin MIM-cap

Going back to ruth brain’s talk, she also said:

“moving up to the metal stack, a new thin barrier reduces via resistance by up to 30%, enhancing interconnect performance. The final innovation is new super-MIM (metal-insulator-metal) capacitor. When compared to the industry standard, it delivers a 5x increase in capacitance in the same footprint, driving a voltage reduction that translates to dramatically improved product performance. … this innovation is enabled by a new class of high-k dielectric materials stacked in ultra-thin layers, just several ångstroms thick, to form a repeating super-lattice structure.”

“we invested significant engineering focus and resources to redesign the metal stack as well. We greatly improved the resistance, the availability, and yield-ability of the mid-layers. We also added two additional high-performance layers at the top, and dramatically enhanced the mim-cap capabilities to ensure a rapid and solid power delivery response for high-CPU intensity workloads.”

So, in the back end we have:

- Thin barriers in the vias, reducing resistance by up to 30%;

- Super MIM-cap with dielectric formed of multiple sub-nanometer layers;

- Two extra high-performance metal layers at the top of the stack

10nm superfin technology combines intel’s enhanced finfet transistors with a super MIM capacitor and an improved interconnect metal stack to deliver performance improvements comparable to a full-node transition, representing the largest single, intranode enhancement in intel’s history. At architecture day in august 2020, intel chief architect raja koduri, intel fellows and architects provided details on the progress intel is making. (credit: intel corporation)

Squinting at the metal stack in the above, I think I can see 18 metal layers, including M0, five more than the initial 10-nm offering in [3], and four more than the first 10-nm slide above, assuming the schematics are accurate. It also appears that the MIM-cap is between M16/M17, and the thin-barrier vias seem to be at M5 and below.

No details were given of course; but I did find a reference for improved via resistance from IITC 2016 – the via dielectric is plasma nitrided before deposition of pure tantalum, giving a thin tan barrier, and reducing via resistance by 30% [4]. I’m tempted to wonder if the new selective tungsten gap-fill technology from the applied materials endura volta system may be being introduced, but that would be zero barrier, and it’s likely a bit early for volume introduction.

The ångstroms-thick layers of the super MIM-cap reminded me of another applied materials launch, at last year’s semicon west. This was the endura clover MRAM PVD platform, specifically designed for the “precise deposition of at least 30 different layers of material, some of which are 500,000 times thinner than a human hair”. If you take a human hair thickness as

100 µm, that means layers

Given that MRAM materials can also have healthy dielectric constants, it seems likely that such a system could be used for the super MIM-cap. Or there’s regular ALD, as used in DRAM dielectrics, which have ZAZ (zirconia/alumina/zirconia) layers in the capacitors. The figure below shows a comparison of the schematics:

By my count there are 32 layers in the intel schematic, so with 2Å layers

6.4 nm total thickness if the schematic is accurate. The inset TEM shows a three-layer capacitor, with what looks like tin electrodes; the dark lines are the dielectric layers, presumably with the multi-layer structure. On the right the applied materials schematic illustrates the multi-layer MRAM stack formed by the clover system.

The last change mentioned was the extra two high-performance metal layers at the top of the stack; given that they should be the largest, they should be relatively high performance, though there could be tweaks like tuning the grain structure, or adding cap/liner layers to improve electromigration properties.

Taken together, intel claims that the transistor, capacitor, and metal stack changes make the largest single intra-node improvement in the company history,

18% according to the plot below.

Also coming up, there is already an “enhanced superfin” variant being developed with yet more optimized transistors and changes to the metal stack, aimed at data centre products.

Nomenclature

As we noted above, at the 14-nm generation the ‘+’ notation became definitely clunky, and at 10-nm we got even more confused with the brief introduction of the cannon lake product. It now appears that intel is regarding the ice lake process as the baseline, so the superfin version is the equivalent of 10+ (cannon lake was 10- ?).

“in fact, during 14-nm generation, there were so many pluses, that we often internally mixed up the actual plus count. Left unchecked, we were going down the same path with our intranode improvements in 10-nanometer. … so we decided, internally, to stop using the plus-plus nomenclature, and get to a descriptive and memorable name to denote and celebrate significant internal enhancements. Taking advantage of the supermim capacitor and the enhanced finfet, we decided to call the generation of transistors superfin.”

To me, superfin as a name implies only changes to the transistor, even just the fin of the transistor, and gives no clue to the other innovations in the back end, so it’s almost as confusing as the plus terminology. It is a convenient abbreviation, though – 10SF is like the foundries’ 7FF or 7LPP, and could morph to 10ESF or 10SFE for the enhanced version. We’ll see if it survives…

The debut of 10SF will be in the tiger lake soc, due to be launched on 2 nd september, and I guess they’d like to have the laptops in stores for the holiday period. We look forward to it!

Addendum – agilex FPGA

The week after the architecture day, the hot chips 32 virtual conference took place, and intel presented on their agilex FPGA family, and noted that they use a customized 10-nm process.

It doesn’t appear that this pushes into the 10SF upgrade, but will be yet another variant to watch for, now they have started shipping.

Intel's path forward: 10nm superfin technology, advanced packaging roadmap

Intel's architecture day 2020 was awash in new revelations, you can find the full breakdown here, but its new 10nm superfin technology and advanced packaging technology rank among the highlights. Both of these technologies will be critical factors as the chipmaker looks to defray the impact from the fallout of its delayed 7nm node.

Intel says the new 10nm superfin technology provides the largest intra-node performance improvement in the company's history, giving its forthcoming chips higher frequencies and lower power consumption than the first version of its 10nm node. That's a critical need because the company had originally planned for a rapid transition to its 7nm process, leaving its generally unproductive and troublesome 10nm node in the rearview mirror while reserving the node for only a few products as the company quickly moved forward to what it saw as the better node.

That rapid transition is obviously delayed now that intel has identified a 'defect mode' in its 7nm process that puts it a year behind its yield targets. Intel says that, due to a buffer designed into its roadmap, the year-long recovery translates to a six-month delay in 7nm products reaching the market. However, intel hasn't specified whether or not those first 7nm products will come with its own process node, or instead from chips bought from external foundries. The latter is a new possibility now that intel has new plans to more aggressively leverage external fabs. That could even result in it using other fabs for its core logic, like cpus and gpus, which the company hasn't done in the past.

To help blunt the blow of the 7nm delay, intel announced that it would boost its 10nm production by 20% over its prior projections and said it planned to wring out another "full node" of performance from the troubled node. It also plans to leverage its advanced packaging technology to rapidly integrate chips produced at third-party foundries into its own products. Both of these technologies are going to be incredibly important as intel strives to remain competitive in the face of ever-growing pressure from all sides in its key money-making segments; the desktop PC and data centers. Both segments are now under attack from a resurgent AMD and the burgeoning ARM ecosystem.

Intel's 10nm superfin technology

Intel's plans to wring out more performance from its 10nm aren't entirely surprising - the company learned the value of inter-node improvements the hard way during its incessant 10nm delays. Through a long string of "+" revisions to its 14nm node, with each step powering performance enhancements throughout the skylake, kaby lake, coffee lake and cooper lake iterations of intel's chips. Each intra-node step yielded a 3.8% to 5.9% improvement in transistor performance at iso leakage, which translates to tangible performance benefits that helped intel remain competitive despite its continuous 10nm delays. In fact, intel claims that it has extracted nearly enough extra performance from 14nm as it has historically gotten from a move to a new, denser process node.

After four intra-node enhancements, much to the amusement and confusion of industry observers, intel is now on its 14nm++++ node. Intel obviously didn't plan for this many iterations of the node when it first slapped the "+" branding on its first 14nm enhancement, and the scheme has become more than unwieldy. In fact, due to rampant confusion about the naming scheme, including among intel's own teams, the company will now assign a new unique name to each process node.

"10nm superfin" marks the first outing for its new terminology, but intel says the node is the equivalent of a 10nm+ revision. Intel says that the name "superfin" comes from a combination of supermim, one of the key ingredients to the design that we'll cover below, and finfet, which is intel's term for its first 3D transistor design that debuted three generations ago and carries on to today.

Intel's inaugural 10nm node encountered plenty of problems, necessitating a lengthy redesign process to fix several not-yet-explained issues. Intel tells us that its currently-shipping version of 10nm still uses cobalt, contact over active gate (COAG), and self-aligned quad patterning (SAQP). This trio of new technologies enabled a 2.7X density improvement over 14nm, but have been rumored to be the source of intel's delays.

Intel's 10nm superfin builds on those technologies with several steps forward of its own. Intel improved the gate pitch to enable higher drive current for some high-speed functions, and enhanced epitaxial growth on the source and drain elements helps lower resistance and improve strain. That helps more current flow through the channel, allowing charge carriers to move more quickly.

The 10nm superfin transistors have a new thin barrier that reduces interconnect resistance by 30%, which improves interconnect performance - a critical factor as interconnects continue to shrink and become one of the largest barriers to chip scaling. Intel claims the supermim (metal-insulator-metal) capacitor brings a 5X improvement in MIM capacitance compared to the "industry standard" devices that have the same footprint. This helps combat vdroop, which helps ensure longer sustained frequency potential. Intel says it used new hi-K materials stacked in a repeating superlattice structure, and also added two high-performance layers to the top of the stack. The changes don't impact density, but have a big impact on performance.

The 10nm superfin transistors offer higher clock speeds at any given voltage, and can operate at a lower voltage at any given frequency. The transistors also have a greater dynamic range from the vmin to vmax (minimum/maximum voltage), and vmax extends further than found with the original 10nm transistors. By tuning the architecture to exploit the full dynamic range of the transistors, intel claims tiger lake offers both higher maximum frequencies in thermally-unconstrained use and is faster and more efficient in TDP-limited environments. Intel says the culmination of the tuning imparts a greater-than-generational performance improvement from the marginally IPC-optimized willow cove core over the sunny cove cores present in ice lake.

Intel says the net effect is the same amount of performance uplift that the company would normally expect from a whole series of intra-node "+" revisions, but with just one iteration. Intel claims these transistors mark the largest single intra-node improvement in the company's history.

Intel famously encountered issues with its original 10nm node that necessitated a redesign, so speculation will run rampant that many of the new features are merely borne of the need to fully correct the issues that hindered first-gen 10nm's performance and profitability.

Regardless, intel claims to have gained a step-function improvement in the 10nm process node, and the improvements have caught the attention of the company's data center architects. Koduri said that the company is working on a new tentatively-named "enhanced superfin" process, optimized specifically for the data center, that will bring about further performance and interconnect improvements. The latter is an important consideration for data center chips that rely on the utmost bandwidth between compute-heavy cores and heavily-utilized I/O interfaces.

Intel says this process tech will debut with the company's rambo cache in its xe ponte vecchio cards and its sapphire rapids data center chips.

Decoupling architecture from process nodes

Intel's struggles with its 10nm node led the company to rethink its approach to chip design completely. In the past, intel's design methodology was focused on single-die monolithic designs with architectures tightly coupled and tuned to each specific process node. Unfortunately, this left the chipmaker exposed to the fallout of any delays in its race to smaller, denser nodes.

Intel is frank that the deep bonds between architectures, IP, and specific process nodes cost it the ability to bring new architectures, like sunny cove, to market within a reasonable time frame. Intel also lost the ability to introduce critically important new features in a timely fashion, like pcie gen 4, creating deficiencies in its product stack. The lack of flexibility also delayed the rapid development of newer types of products, like its xe graphics. The tight coupling between architecture and process nodes also made it nearly impossible to port those designs over to older process nodes, or to shift its designs to nodes from other foundries.

Intel's initial set of contingency plans marked a transformational change to the company's design methodologies. First, intel committed itself to decoupling its architectures from the process, thus making its architectures portable between nodes. This new approach allows the chipmaker to use newer architectures on older nodes, thus speeding deployment in the face of unanticipated delays. It also allows intel to select the best node for the intended purpose, be it either an internally-developed node, or a node from an external vendor.

These changes do result in sacrificing some level of deep architectural tuning for each process node, which in turn results in less performance-enhancing customizations. However, the net effect is a faster, more flexible design process that allows the company to sidestep challenges with its process tech.

Superforex review

Superfin corp

Superforex is a forex broker. Super forex offers the metatrader 4 forex trading top platform. Superforex.Com offers over 100 currency pairs, cfds, indices, energy, gold and silver for your personal investment and trading options.

Broker details

| established: | 2013 |

| address: | 5 cork street, 2 floor, belize city, belize |

| contact: | support@superforex.Com, +65-3-1590282 |

| regional offices: | |

| regulators: | IFSC #IFSC/60/292/TS/14 |

| prohibited countries: |

| deposit methods: | bank wire, VISA, mastercard, bitcoin, epayments, fasapay, flutterwave, ipay, litecoin, local bank transfers, neteller, ngan luong, onlinenaira, payco, payeer, perfectmoney, qiwi, skrill, sticpay, triv, unionpay |

| withdrawal methods: | bank wire, VISA, mastercard, bitcoin, epayments, fasapay, flutterwave, ipay, litecoin, local bank transfers, neteller, ngan luong, onlinenaira, payco, payeer, perfectmoney, qiwi, skrill, sticpay, triv, unionpay |

Live discussion

Join live discussion of superforex.Com on our forum

Video

Let other traders know if this service is worth checking or should be avoided.

Traders reviews

This is only to show that you keep lieing for free:

Account: 3015483

name: mihai sebastian onocan currency: EUR

leverage: 1:1000 2020 december 21, 23:59

Closed transactions:

ticket open time type volume item price S / L T / P close time price commission swap profit

369077 2020.12.21 13:49:26 sell 4.00 gbpusd 1.32727 0.00000 0.00000 2020.12.21 21:09:30 1.34031 0.00 0.00 -4 258.97

369079 2020.12.21 13:49:26 buy 4.00 gbpusd 1.32704 0.00000 0.00000 2020.12.21 17:23:01 1.33090 0.00 0.00 1 264.10

369419 2020.12.21 17:23:01 buy 4.00 gbpusd 1.33062 0.00000 0.00000 2020.12.21 19:47:01 1.33354 0.00 0.00 954.96

369566 2020.12.21 19:47:01 buy 4.00 gbpusd 1.33343 0.00000 0.00000 2020.12.21 21:09:36 1.34212 0.00 0.00 2 837.92

369630 2020.12.21 21:09:31 sell 4.00 gbpusd 1.34058 0.00000 0.00000 2020.12.21 21:09:52 1.34524 0.00 0.00 -1 521.54

369691 2020.12.21 21:09:36 buy 4.00 gbpusd 1.34176 0.00000 0.00000 2020.12.21 21:09:53 1.34614 0.00 0.00 1 430.39

369693 2020.12.21 21:09:53 sell 4.00 gbpusd 1.34623 0.00000 0.00000 2020.12.21 21:10:23 1.34558 0.00 0.00 212.25

369695 2020.12.21 21:09:53 buy 4.00 gbpusd 1.34593 0.00000 0.00000 2020.12.21 21:24:18 1.34830 0.00 0.00 774.14

369697 2020.12.21 21:10:23 sell 4.00 gbpusd 1.34578 0.00000 0.00000 2020.12.21 21:16:55 1.34377 0.00 0.00 656.46

369701 2020.12.21 21:16:58 sell 4.00 gbpusd 1.34394 0.00000 0.00000 2020.12.21 21:21:34 1.34494 0.00 0.00 -326.70

369713 2020.12.21 21:21:35 sell 4.00 gbpusd 1.34546 0.00000 0.00000 2020.12.21 21:24:18 1.34877 0.00 0.00 -1 081.02

369725 2020.12.21 21:32:07 buy 6.00 gbpusd 1.34972 0.00000 0.00000 2020.12.21 22:15:11 1.34556 0.00 0.00 -2 038.57

369726 2020.12.21 21:32:07 sell 6.00 gbpusd 1.34971 0.00000 0.00000 2020.12.21 22:15:12 1.34579 0.00 0.00 1 920.64

824.06closed P / L:

open trades:

ticket open time type volume item price S / L T / P close time price commission swap profit

368735 2020.12.21 12:13:06 sell 0.30 eurusd 1.21488 0.00000 0.00000 1.22465 0.00 0.00 -239.33

368737 2020.12.21 12:13:10 buy 0.30 eurusd 1.21478 0.00000 0.00000 1.22436 0.00 0.00 234.73

369537 2020.12.21 19:02:09 buy 0.01 usdcad 1.28353 0.00000 0.00000 1.28563 -0.05 0.00 1.34

369539 2020.12.21 19:02:09 sell 0.01 usdcad 1.28423 0.00000 0.00000 1.28581 -0.05 0.00 -1.01

-4.37floating P / L:

working orders:

ticket open time type volume item price S / L T / P market price commission

no transactions

summary:

deposit/withdrawal: 0.00 credit facility: 0.00

closed trade P/L: 824.06 floating P/L: -4.37 margin: 107.04

balance: 5 115.57 equity: 5 111.20 free margin: 5 004.16

thank you for choosing superforex!

JUST CHECK THE DAYLI CONFIRMATION EMAIL BEFORE YOU SAID THAT YOU CHECKED MY ACCOUNT

I HAVE THE SAME ADVISE , STAY AWAY!

Dec 29, 2020 - 1 star hi,

my advice is to stay away from this broker, it is by far one of the most terrible experiences with a broker.

After I made a profit, my account was manipulated by super forex, and they wiped out my account in 3 days in two days from more than 5000 euros to 0. The only place where they did not cover their fraudulent method is in dayli statements, received by email. I sent them several emails and they don't answer at all.

Below I attach some information.

Account: 3015483

name: mihai sebastian onocan currency: EUR

leverage: 1:1000 2020 december 21, 23:59

deposit/withdrawal: 0.00 credit facility: 0.00

closed trade P/L: 824.06 floating P/L: -4.37 margin: 107.04

balance: 5 115.57 equity: 5 111.20 free margin: 5 004.16

Name: mihai sebastian onocan currency: EUR

leverage: 1:1000 2020 december 22, 23:59

deposit/withdrawal: 0.00 credit facility: 0.00

closed trade P/L: -478.78 floating P/L: -1.07 margin: 5.34

balance: 368.48 equity: 367.41 free margin: 362.07

As you can see from a day to another there are missing more than 4000 euro, and in 23.12 they wiped out all the account money:

account: 3015483

Name: mihai sebastian onocan currency: EUR

leverage: 1:1000 2020 december 23, 23:59

deposit/withdrawal: 18.68 credit facility: 0.00

closed trade P/L: -324.72 floating P/L: 0.00 margin: 0.00

balance: 0.00 equity: 0.00 free margin: 0.00

Reply by superfx_official submitted jan 5, 2021 hello, we've checked your account. You opened risky trades with high volume. Some orders reached 40 lots. Your last trades were just unprofitable, we can't really do anything here.

Also we didn't see the amount of 5000 EUR ever recorded on your account balance.

Your review just isn't true.

Hello. Indeed, the part of your profits got canceled due to prohibited trading strategy based on the technical imperfections of the trading platform MT4.

You have successfully withdrawn your full deposit and the part of achieved profits.

Superforex is still a fraud, they did not return my deposit money completed, after cancelling all my profits, the company now charged my account again.

There's no way the company can continue in business again by defrauding clients.

Nov 23, 2020 - 1 star last month, october, 2020, superforex defrauded me of my hard-earned money to the tune of $1500, they cancelled all the profits I made in the month of october, 2020 and then charged my account again.They were able to do this because they don't have an office in my country, I would have charged them to court.

If they know that you deposit huge amount of money for trading, all they will be looking for is to deprive you of your hard-earned money. I have told them that they cannot go free god will surely judged them.

Reply by superfx_official submitted dec 17, 2020 hello, your trading strategy is based on the imperfections of the trading platform. We did cancel your profits several times and informed you that such strategies are not allowed.

We returned to you your deposit funds in full amount.

Hello, your account has 1:1000 leverage. You did not apply for any bonus.

Your trades were unsuccessful, that's why your balance went down.

We just don't see any reason to call superforex scam, based on your review.

Also, please check the FAQ page if you want to change your leverage. Support managers can help with this as well.

Https://superforex.Com/faq

I have invested mainly in the purchase of SPN35 and CL, well as these symbols have gone up and my earnings should increase, the opposite has happened my earnings have decreased, I contacted them and they told me that they modified the lots and that they had the right to do it in the middle of trading.

Well then yesterday when the symbol SPN35 was falling multiplied the balance of losses by 20 so that the account go to 0

An example: ticket 866234676 price buy: 7527.1, current price: 7390.2, volume 0.01 on june 23 gave me a loss of -24.20,

the next day ticket 866234676 price buy: 7527.1, current price: 7117.8, volume 0.01 on june 24 gave me a loss of -726.62 €

as you can see it is disproportionate.

Yesterday i have contacted with superforex them and received no response.

Today i contacted IFSC and first i will wait a answer. When they respond to me, I will ask them for advice and it is possible that will take this issue to an expert lawyer and use the necesary money to find these people.

Hello, you can email dealer@superforex.Com if you still have questions.

As for #CL trading symbol we didn't change settings for that. You can always check trading result with independent online calculator. For example this one: https://www.Investing.Com/tools/profit-calculator

as for SPN35 we recently changed the lot size from 10 to 1 to let you open more deals. All you need is to open more volume of the deal. You can always check trading result with independent online calculator. For example this one: https://www.Investing.Com/tools/profit-calculator

Profit calculator - investing.Com

https://www.Investing.Com

Length of use: over 1 year

The entire superforex is controlled by their CEO vladmir syrov who is the perfect definition of scam and fraud. They are heartless. They scammed me when depositing $53,000, and $34,000 when trading, and a further $2,572.67 which they refused to allow me to withdraw. I want to give them zero star in the rating but there was no option rather than one star as the minimum.

Please do not use their so called country representatives, local currency depositors or official partners to make deposits as it was the case with me when vladmir syrov introduced me to one of their company company staff called collins mark to process my deposit and he later defrauded me of my $53,000 when he connived with the company and did not credit my trading account. The company is now denying that he is not their staff but rather an agent hence they are not going to compensate me.

The entire customer service experience with superforex is also very poor, and the staff including the CEO are very unprofessional in their dealings and communications. Would like to clearly state that superforex have lied to me on several occasions, and they are very rude, dishonest, deceitful and evasive in their dealings. They employ dirty tactics and everything by hook or by crook to rip people off their money.

Their systems do not operate automatically as they manually manipulate their systems to ensure that you lose your money. They manipulate the prices, spread, margin call, and stop out to ensure that they make maximum profit from your losses.

It is just a shame that I never read the reviews otherwise I would not have ever traded with them in the first place. I stand fully responsible for my statement as I have already been in contact with the CEO vladmir syrov and the company on several occasions to resolve my complaint but to no avail. I am confidently calling him a fraudster and you can contact me for more information and evidence to validate my claims. I have already invited the company to the forex peace army court to resolve my complaint but they are not responding.They claim to be regulated by the IFSC in belize but it is just a sham and regulatory system where the regulator has no control of the financial companies in the country. Be aware that belize is one of those tax havens with relaxed financial control. I have contacted the IFSC and they have not done anything about my complaints so do not hope that you would be able to have your complaints resolved by the country regolulator when you have been defrauded by superforex.

The company also has very loose terms and conditions which they claim to be the solution to all complaints. They would give no explanations and would avoid discussing your complaints by referring you to the T&cs. Be rest assured that referral to the vague T&C's would be the only response you get when you make any complaints and you would be speaking to a dead wall when you challenge back. They have fake departments which only exist by email called dealer, and risk management and trading, to deal with your complaints but in reality they are all controlled by the CEO vladmir syrov whose main aim is to cheat and defraud you of your money. He even writes the responses on behalf of the fake departments. The company goes as far as paying people to write fake positive reviews for them. Please do not wait to become a victim, avoid this company by all means possible. This is a warning for everybody to stay clear of superforex. They are big FRAUDSTERS and SCAMMERS.

May 11, 2020 - 1 star the entire superforex staff are controlled by their CEO vladmir syrov who is the perfect definition of scam and fraud. They are heartless. They scam you when depositing money, when trading, and when making withdrawals. I wish I could give them zero star in the rating but there was no option rather than one star as the minimum.

The entire customer service experience with superforex is very poor, and the staff including the CEO are very unprofessional in their dealings and communications. Would like to clearly state that superforex have lied to me on several occasions, and they are very rude, dishonest, deceitful and evasive in their dealings. This is a warning for everybody to stay clear of superforex. They are a big SCAM.

It is just a shame that I never knew of the forex peace army and their superforex review otherwise I would not have ever traded with them in the first place. You can read my full story under the scam thread:

Reply by superfx_official submitted may 18, 2020 be informed that mark collins never being our employee, he was local agent and we did not bear any responsibility for activity of 3rd party https://front.Supercdn.Site/documents/superforex-ltd-hot-bonus-agreement-en.Pdf

In the same time we have already reported to nigeria police department in order to help you with that case and solve it succesfully and in the same time please be aware, that according client tnc we are not responsible for 3rd party according clause 9.14:

9.1.4. The customer acknowledges that the company or a third party involved in providing the services to the customer shall not be liable for malfunctioning of the telephone or internet equipment, scheduled maintenance or updates or any other events beyond the control of the company or information service providers or a third party providing services to the customer.

But in any case we are helping you in this issue and everyday working with officers in lagos for solving it.

Regarding your other terms from the claim, your strategy was extremely high and company does not bear responsibility for the result of your trading.

Pls read 7. Risks from client agreement. Https://front.Supercdn.Site/documents/superforex-ltd-client-agreement-en.Pdf

Regarding bonus issue - you should also read terms of bonus and be aware that hot bonus 202% is an exclusive offer and profit generated by using this bonus is distributed accordingly. According your trading result in the beginning you generated profit and part of this profit was distributed to bonus funds (read terms of hot bonus here - https://front.Supercdn.Site/documents/superforex-ltd-hot-bonus-agreement-en.Pdf). Then according our checks you had a huge drop down and when margin level becomes lower then 300% bonus can be cancelled including part of the profit generated by using this bonus.

You should always rely only on your funds in trading strategies.

Is a smaller manufacturing process always better? Intel’s 10nm superfin suggests otherwise

How open banking is driving huge innovation

Learn how fintechs and forward-thinking fis are accelerating personalized financial products through data-rich apis.

This article is part of the technology insight series, made possible with funding from intel.

When it comes to manufacturing technology, we’re taught that smaller transistors are better. They switch faster and use less power. They take up less space, carving out room for more cores, more cache, and ultimately better performance. And when foundries can fit more dies onto the same sized silicon wafer, costs go down. It’s no surprise that the technology world anticipates each process shrink with bated breath.

But not all nodes are created equal. Back in 2017, mark bohr, intel’s former director of process architecture and integration, claimed the company’s 14nm process had about a three-year lead over the competition’s 10nm technology with similar density. In this case, density refers to the number of transistors packed into a unit of area (typically square millimeters). Interestingly enough, he also showed that enhanced versions of intel’s 14nm node would actually outperform its first 10nm effort, albeit at higher active power consumption.

Today, enhanced 10nm transistors play a key role in helping intel’s new tiger lake mobile platform hit higher clock rates compared to the previous-gen ice lake design. The transistors are simultaneously faster and more efficient than any preceding process, rivaling the competition’s 7nm technology. How is such a thing possible? Intel says it’s focusing on manufacturing innovations beyond traditional feature scaling, such as new materials and device architectures. Intel calls the resulting node 10nm superfin.

“the combined power of these innovations enable us to deliver a dramatic processor performance boost that makes it the largest single node enhancement in intel history,” says dr. Ruth brain, intel fellow in the technology and manufacturing group. Let’s take a closer look at the technologies supercharging the 10nm process with what dr. Brain claims is nearly the equivalent performance of a full node transition.

Key points

- The 10nm superfin node is a long-awaited enhancement to intel’s first 10nm manufacturing process

- Intel implemented a number of innovations beyond smaller transistor features to realize major gains

- A planned 10nm enhanced superfin process will be tailored for data center cpus and gpus

Performance and power are more than just the node name

Once upon a time, nodes were referred to by minimum feature size—typically the transistor gate length, or the distance electrons travel from the transistor’s source to drain. This changed gradually as as other parts of the transistor got smaller and gate lengths stopped scaling as aggressively.

Above: as far back as 2017, we knew it’d take a couple of node enhancements for intel’s 10nm technology to surpass the mature 14nm process.

Today, node names largely represent generational progress. They don’t reflect gate length; the pitch, width, or height of modern field-effect transistor (FET) fins; or even transistor density. It’s consequently difficult to cut through the marketing and compare competing process technologies based on their names.

But because intel struggled to bring 10nm to production, the company must now endure contrasts between its 10nm transistors and the 7nm nodes from TSMC and samsung. Fortunately for intel, the 10nm node holds its own, even though naming suggests otherwise. Heavy investment into beefing up 10nm helped intel facilitate a

2.7x density improvement over 14nm, packing more than 100 million transistors into a square millimeter of die area.

“the aggressive scaling was enabled by innovations that moved beyond the transistor device to the metal interconnects and ultimately cell level and beyond,” said brain at intel’s recent architecture day 2020.

The long road to 10nm

One such innovation is self-aligned quad patterning, a process used to overcome lithography resolution limits and create very dense interconnects. Intel’s 10nm node is the first to use self-aligned quad patterning on the lowest metal layers to drive interconnect pitch scaling from 52nm at 14nm manufacturing down to 36nm, bringing the wires connecting transistors closer together.

Those same metal layers also employ cobalt local interconnects for the first time, reducing the effects of electro-migration and halving via resistance compared to copper at the narrowest interconnect pitches.

Intel’s 10nm process incorporates contact over active gate (COAG) technology, too. According to kaizad mistry, co-director of logic technology development at intel, moving the contact from its traditional position next to the transistor to right above it improves area scaling by 10%.

Above: contact over gate technology is one of the features of intel’s 10nm process, which helps improve area scaling by roughly 10%.

Further density scaling at 10nm is achieved by halving the number of spacer, or dummy gates, between cells. At 14nm, intel used one dummy gate at each end of its cell. With two cells side by side, that looked like a pair of adjacent dummy gates. Now cells can share one gate, delivering an additional

Refining the technologies that went into intel’s 10nm process did delay volume production more than the company would have liked. However, they ultimately laid a foundation for the enhancements found in 10nm superfin. “the era of getting massive performance boosts from simply shrinking transistor features is behind us,” brain said. Now, improvements made to the process stack promise a substantial boost.

10nm superfin = supermim + redefined finfet

After years of tacking pluses onto its 14nm intranode enhancements, intel is being a little more creative with its nomenclature. 10nm superfin is derived from a new super MIM (metal-insulator-metal) capacitor design and what the company calls a redefined finFET.

Above: some of the 10nm superfin’s improvements focus on enhancements to intel’s transistor design.

“within the transistor, we improved epitaxial growth of crystal structures on the source and drain, increasing the strain and decreasing resistance,” said brain. As a result, more current can flow through the channel. Enhancements to the finfet’s source and drain architecture further improve channel mobility, enabling charge carriers like electrons to move more quickly. Moreover, a larger gate pitch creates an opportunity for higher drive current, servicing performance-sensitive chip functions. Together, those transistor-level improvements allow 10nm superfin to hit higher clock rates at any set voltage compared to intel’s original 10nm process.

The 10nm superfin process uses thinner barrier materials that reduce vertical interconnect access (via) resistance by 30%. If you’re interested in some heavy reading, check out this presentation by dr. Paul besser at the northern california chapter of AVS back in 2017. But in brief, he points out that resistance is of increasing concern as interconnect pitch scales down (hence the switch to cobalt for certain metal layers). Using new barrier materials for 10nm superfin further address the resistance problem, improving interconnect performance.

Above: the super MIM cap increases capacitance by up to 5x, intel claims. The result is a voltage reduction that improves performance.

Even more significant is the super MIM capacitor, which intel says increases capacitance by 5x compared to the industry standard. “this innovation is enabled by a new class of hi-K dielectric materials stacked in ultra-thin layers just several angstroms thick to form a repeating superlattice structure,” said intel’s brain during her presentation. The capacitance increase enables a voltage reduction that, again, pays dividends in performance.

Putting rubber to the road with tiger lake

With just one intranode enhancement, 10nm superfin delivers gains almost equivalent to a full node transition, the company claims. If that proves true, the tiger lake system-on-chip (soc) due out this year and built using 10nm superfin should be formidable.

Intel says it optimized tiger lake for the 10nm superfin process. So, the soc’s quad-core willow cove CPU is free to hit dramatically higher frequencies within the same power envelopes as its predecessor. That fact alone is expected to confer a greater than generational performance improvement.

Above: in practice, 10nm superfin allows the upcoming willow cove core to operate at higher clock rates for any fixed voltage or reduce voltage at a given frequency.